# PSIA-2722

### Programmable Serial Interface Adapter

## PSIA-2722 User's Manual

Installation and Operation of the Audio Precision Programmable Serial Interface Adapter Copyright © 2002-2005 Audio Precision, Inc.

All rights reserved.

Audio Precision part number 8211.0159 Rev 1

No part of this manual may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or by any information storage and retrieval system, without permission in writing from the publisher.

Audio Precision®, System One®, System Two™, System Two Cascade<sup>™</sup>, System One + DSP<sup>™</sup>, System Two + DSP<sup>™</sup>, Dual Domain<sup>®</sup>, FASTTEST<sup>®</sup>, APWIN<sup>™</sup>, 2700 Series, AP2700, ATS<sup>™</sup> and ATS-2<sup>™</sup>are trademarks of Audio Precision, Inc. Windows is a trademark of Microsoft Corporation.

Published by:

5750 SW Arctic Drive email: info@audioprecision.com

### Contents

| Safety Information                           |      |

|----------------------------------------------|------|

| Safety Symbols                               | vi   |

| Chapter 1                                    |      |

| ntroduction                                  | 1    |

| Capabilities                                 |      |

| Transmitter and Receiver                     | 2    |

| Data and Clock ports                         | 2    |

| Data settings                                | 3    |

| Voltage levels                               | 3    |

| Documentation                                | 4    |

| Chapter 2                                    |      |

| nstallation and Setup                        |      |

| PSIA-2722 Components                         |      |

| Power Supply                                 |      |

| PN 4540.0020                                 | 6    |

| PN 4540.0051                                 |      |

| Connecting the PSIA to the instrument        | 7    |

| Chapter 3                                    |      |

| Converter Testing.                           |      |

| Relationship between PSIA and the instrument |      |

| PSIA Transmitter and Receiver Connections    |      |

| Connect an oscilloscope                      |      |

| Connections for Loop-Back configuration      |      |

| Connections for ADC testing.                 |      |

| Connections for DAC testing.                 |      |

| Connections for SRC testing.                 |      |

| The Transmitter and Receiver panels          |      |

| Transmitter and Receiver Settings            | . 18 |

| Duplicated Controls and Displays                       |  | . 19 |

|--------------------------------------------------------|--|------|

| Channel Data Assignment                                |  | . 20 |

| One-click I <sup>2</sup> S bus settings                |  | . 20 |

| Transmit Data Clock Edge                               |  | . 21 |

| PreEmphasis (Transmitter only)                         |  | . 22 |

| DeEmphasis (Receiver only).                            |  | . 22 |

| Scale Freq. by                                         |  | . 22 |

| Audio frequency scaling                                |  | . 22 |

| Rate Ref                                               |  | . 22 |

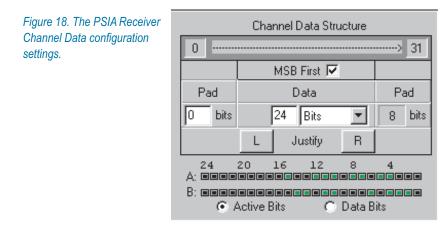

| Channel Data                                           |  | . 23 |

| Bits per channel display                               |  | . 23 |

| MSB first: Transmitter                                 |  | . 24 |

| MSB first: Receiver                                    |  | . 24 |

| Data and padding controls                              |  | . 25 |

| Data                                                   |  | . 25 |

| Pads                                                   |  | . 25 |

| Left and Right Justify: Transmitter                    |  |      |

| Left and Right Justify: Receiver                       |  | . 26 |

| Pad bits logic states (Transmitter only)               |  |      |

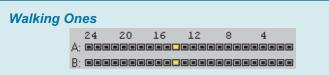

| Data Bit Indicators                                    |  | . 26 |

| The Clocks control matrix                              |  | . 27 |

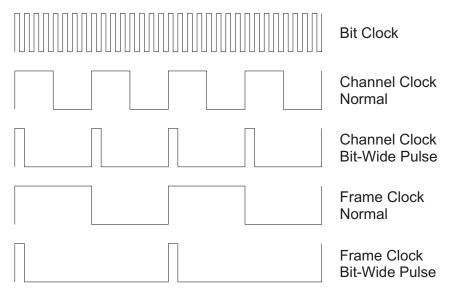

| The Clock signals                                      |  |      |

| The Clock controls                                     |  |      |

| Direction                                              |  |      |

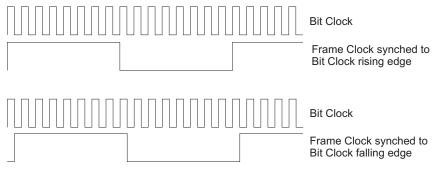

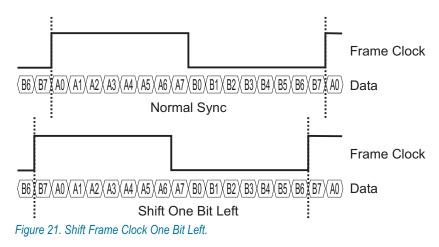

| Bit Clock Edge Sync (Frame Clock and Channel Clock)    |  | . 28 |

| Invert Waveform (Frame, Channel and N*Fs Clocks)       |  |      |

| Shift One Bit Left (Frame Clock Only)                  |  |      |

| Bit Wide Pulse (Frame Clock and Channel Clock)         |  |      |

| PSIA Clock Rate and Factor Settings                    |  |      |

| Frame Clock (Fs) Rate Setting                          |  |      |

| Channels per Frame.                                    |  |      |

| Setting the Bits per Channel                           |  | . 32 |

| N, the N*Fs multiplier                                 |  |      |

| M, the Master Clock multiplier                         |  |      |

| Jittering the Master Clock                             |  | . 33 |

| Computed Clock Rate Displays                           |  | . 33 |

| Logic Voltage controls                                 |  | . 34 |

| PSIA Quick Setup Guide                                 |  | . 34 |

| Common converter testing configurations                |  | . 36 |

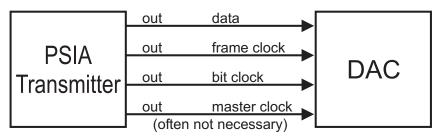

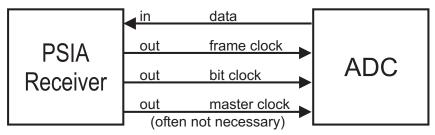

| PSIA Transmitter: Frame, Bit & Master Clock OUT        |  | . 36 |

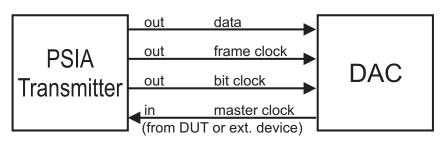

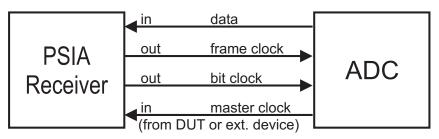

| PSIA Transmitter: Frame & Bit Clock OUT, Master Clk IN |  |      |

| PSIA Receiver: Frame, Bit & Master Clock OUT           |  |      |

| PSIA Receiver: Frame & Bit Clock OUT, Master Clock IN  |  | . 37 |

#### **Appendix A**

| Miscellany                       |  |   |       |   |       |   |   |   |   |   |         | 39 |

|----------------------------------|--|---|-------|---|-------|---|---|---|---|---|---------|----|

| PSIA Abbreviations and Terms     |  |   |       |   |       |   |   |   |   |   | <br>    | 39 |

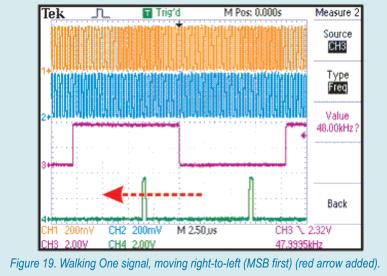

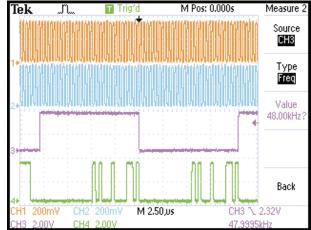

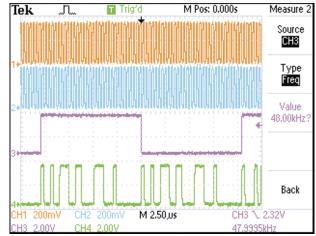

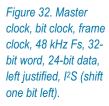

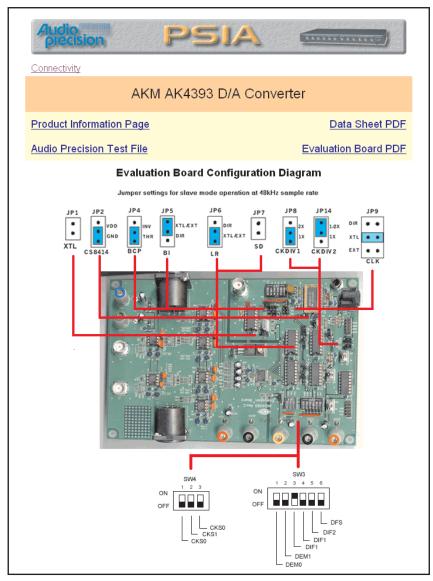

| Oscilloscope Examples            |  |   |       |   |       |   |   |   |   |   | <br>    | 40 |

| N*Fs Table                       |  |   |       |   |       |   |   |   |   |   | <br>    | 42 |

| Using INTERVU with PSIA-2722     |  |   |       |   |       | • |   |   |   |   | <br>    | 42 |

| Appendix B                       |  |   |       |   |       |   |   |   |   |   |         |    |

| Configuration Examples and Files |  |   |       |   |       |   |   |   |   |   |         |    |

| Eval boards and sample files     |  | · | <br>• |   | <br>• |   | • | • | • | • | <br>• • | 43 |

| Appendix C                       |  |   |       |   |       |   |   |   |   |   |         |    |

| Connection Guidelines            |  |   |       |   |       |   |   |   |   |   |         |    |

| General Guidelines               |  |   |       |   |       |   |   |   |   |   |         |    |

| Oscilloscope Monitoring          |  |   |       |   |       |   |   |   |   |   |         |    |

| Triggering                       |  |   |       |   |       |   |   |   |   |   |         |    |

| Oscilloscope Connections         |  | · | <br>• | • | <br>• | • | • | • | • | • | <br>•   | 46 |

| Appendix D                       |  |   |       |   |       |   |   |   |   |   |         |    |

| Specifications                   |  |   |       |   |       |   |   |   |   |   |         |    |

| DC Characterisics                |  |   |       |   |       |   |   |   |   |   |         |    |

| DC characteristics, no load      |  |   |       |   |       |   |   |   |   |   |         |    |

| PSIA input / output impedance    |  |   |       |   |       |   |   |   |   |   | <br>    | 47 |

| AC characteristics               |  |   |       |   |       |   |   |   |   |   | <br>    | 48 |

| Maximum clock frequency          |  |   |       |   |       |   |   |   |   |   | <br>    | 48 |

| Output latency, Clock to Out     |  |   |       |   |       |   |   |   |   |   | <br>    | 48 |

| Setup and Hold, inputs           |  |   |       |   |       |   |   |   |   |   | <br>    | 49 |

| User test jacks                  |  |   |       |   |       |   |   |   |   |   |         | 49 |

| APIB                             |  |   |       |   |       |   |   |   |   |   |         | 49 |

| APIB configuration maximums      |  |   |       |   |       |   |   |   |   |   | <br>    | 49 |

| Appendix E                       |  |   |       |   |       |   |   |   |   |   |         |    |

| AP Basic Extensions for PSIA     |  |   |       |   |       |   |   |   |   |   | <br>    | 51 |

#### **Safety Information**

Do NOT service or repair this product unless properly qualified. Servicing should be performed only by a qualified technician or an authorized Audio Precision distributor.

One of two external power supplies is provided with this product:

The power supply PN 4540.0020 is designed to operate only from an AC power source (100 V–240 V rms, 47 Hz–63 Hz) with an approved three-conductor power cord and safety grounding. Do NOT defeat the safety ground connection.

The power supply PN 4540.0051 is designed to operate only from an AC power source (100 V–240 V rms, 50 Hz–60 Hz). This power supply has an in-tegral 2-conductor mains plug.

Either power supply automatically adjusts to the line voltage and frequency within the specified range. No user adjustments are necessary. Neither of the power supplies nor the PSIA-2722 contain user-replaceable fuses.

Use only the AP power supply PN 4540.0020 or PN 4540.0051 with the PSIA-2722. The use of other power supplies may result in damage to the PSIA-2722, electrical shock hazard from the power supply or the PSIA-2722, and loss of fire hazard protection.

This product and power supply are for indoor use ONLY.

The following symbols may be marked on the panels or covers of equipment or modules, and may be used in this manual:

WARNING!—This symbol alerts you to a potentially hazardous condition, such as the presence of dangerous voltage that could pose a risk of electrical shock. Refer to the accompanying Warning Label or Tag, and exercise extreme caution.

$\triangle$

ATTENTION!—This symbol alerts you to important operating considerations or a potential operating condition that could damage equipment. If you see this marked on equipment, consult the User's Manual or Operator's Manual for precautionary instructions.

FUNCTIONAL EARTH TERMINAL—This symbol marks a terminal that is electrically connected to a reference point of a measuring circuit or output and is intended to be earthed for any functional purpose other than safety.

PROTECTIVE EARTH TERMINAL—This symbol marks a terminal that is bonded to conductive parts of the instrument. Confirm that this terminal is connected to an external protective earthing system.

### Chapter 1 Introduction

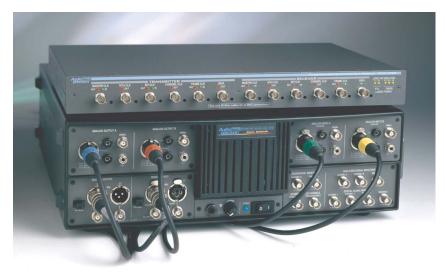

#### Figure 1. The Audio Precision PSIA-2722 Programmable Serial Interface Adapter.

The PSIA-2722 Programmable Serial Interface Adapter is an accessory unit for Audio Precision's System Two Cascade, Cascade *Plus* and 2700 Series digitally-capable instruments. Since the PSIA operations for all these systems are identical, in this manual the designation "instrument" indicates any of the above models.

When used without a serial interface adapter, the instrument can provide AES3 and IEC60958 serial digital inputs and outputs at a wide range of sample rates and resolutions, as well as parallel digital inputs and outputs. A serial interface adapter such as PSIA-2722, however, is required to transmit or receive digital signals and associated clock inputs and outputs for non-AES3/IEC60958 serial formats often encountered in telecommunications and converter design and testing.

The PSIA-2722 is similar in capability to the earlier Audio Precision SIA-2322, with a key difference: the PSIA-2722 is software controlled. Where configuring the SIA-2322 involved the manual setting of a number of DIP switches for each test setup, PSIA-2722 is configured from the PSIA panel in the instrument control software. The setting of master clock rate, N\*Fs clock rate, bit rate, number of channels, word length and sample rate is more intuitive and is aided by automatic calculations. Each test configuration is now

saved as part of the instrument test file. Setups for specific converters can be loaded from previous tests or imported from sample files.

The PSIA-2722 must be connected to an Audio Precision instrument running the appropriate control software:

- For System Two Cascade and System Two Cascade *Plus* instruments, the control software must be APWIN version 2.22 or 2.24, or AP2700. We strongly recommend AP2700 version 3.10.

- For a 2700 Series instrument, the control software must be AP2700.We strongly recommend AP2700 version 3.10.

AP2700 control software is available by download from the Audio Precision Web site at audioprecision.com.

The instrument parallel digital output and input provide data connections for the PSIA; additional cables connect the instrument master clock and the APIB control bus to the PSIA-2722. The PSIA is powered by a separate 5 VDC power supply.

The PSIA provides all necessary serial input, output and clock ports for device connection, as well as provision for oscilloscope monitoring of the various signals. The voltage levels of all the PSIA ports can be set to accommodate devices from different logic families.

#### **Capabilities**

#### **Transmitter and Receiver**

PSIA-2722 has a serial transmitter section for testing devices with digital input, such as DACs; and a serial receiver section for testing devices with digital output, such as ADCs. Each section is configurable to a wide range of clock and data settings, using either internal or external clock references.

The transmitter and receiver sections can also be operated simultaneously for SRC or other testing. When the instrument's internal master clock is used as the only clock in this configuration, the clock rates of the two sections are tightly coupled. When this configuration is used with a second, external master clock (typical of SRC testing), the controls and functions of the transmitter and receiver are almost entirely independent.

#### **Data and Clock ports**

The transmitter and receiver sections each have ports and software panel controls for

- Data

- Frame Clock

- Channel Clock

- Bit Clock

- N\*Fs Clock

- Master Clock

Within certain constraints, the clocks can be set to a wide selection of rates. For SRC testing, transmitter and receiver clocks can be set to different rates when a second master clock frequency is provided. Configuration of clock signal polarity, edge sync, pulse width and sync relation to data is available where appropriate.

The Master Clock, Bit Clock and Frame Clock ports can be configured as inputs or outputs, enabling independent selection of master or slave mode for receiver and transmitter.

#### **Data settings**

For transmission, the data are provided from the instrument as determined by the Digital Generator and Digital I/O settings, and the PSIA configures this data in a serial stream for the device under test (DUT).

For reception, the serial stream comes from the DUT, and the PSIA must be set to match the incoming data configuration.

The arrangement of the data within the serial word can be set or matched by adjusting four parameters:

- The data length in bits,

- The padding bits before and after the data (if any),

- The state of the padding bits,

- The order of the data bits (MSB or LSB first).

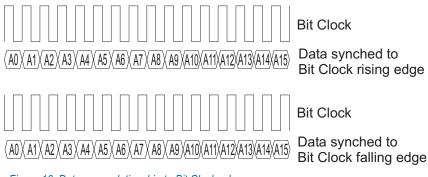

Also, the timing relationship between the data and the bit clock (synchronized on the rising or falling edge) can be set.

#### Voltage levels

PSIA clock and data ports can be set to interface with common logic families:

- 5.0 V TTL

- 3.3 V TTL

- 3.3 V CMOS

- 2.4 V CMOS

- 1.8 V CMOS

#### **Documentation**

This *PSIA-2722 User's Manual* is the primary document for the PSIA. Converter testing also requires a good understanding of many of the functions of the Audio Precision instrument; these are covered in detail in the instrument's *User's Manual*.

Context-sensitive Help information for the PSIA is included within the control software.

Visit the Audio Precision Web site at audioprecision.com for more information on using the PSIA.

### **Chapter 2** Installation and Setup

Figure 2. PSIA-2722 and a System Two Cascade Plus.

The PSIA-2722 is an accessory to Audio Precision's System Two Cascade, Cascade *Plus* and 2700 Series digitally-capable instruments. Since the PSIA operations for all these systems are identical, in this manual the designation "instrument" indicates any of the above models.

The PSIA-2722 must be connected to an Audio Precision instrument running the appropriate control software:

- For System Two Cascade and System Two Cascade *Plus* instruments, the control software must be APWIN version 2.22 or 2.24, or AP2700. We strongly recommend AP2700 version 3.10.

- For a 2700 Series instrument, the control software must be AP2700.We strongly recommend AP2700 version 3.10.

AP2700 control software is available by download from the Audio Precision Web site at audioprecision.com.

See your instrument *Getting Started* manual for information on setting up your Audio Precision instrument.

#### **PSIA-2722 Components**

When you open the shipping box you will find:

- The PSIA-2722 chassis.

- A 5 VDC external universal mains power supply, selected for your location; either PN 4540.0020 or PN 4540.0051. The power supply output cord is attached to the PSIA-2722 chassis.

- If your power supply is PN 4540.0020, there will be a mains cable for the power supply. Power supply PN 4540.0051 has an integral mains plug.

- An APIB cable. This cable is for exchange of control data between the PSIA, the instrument and the controlling PC.

- Two 25-wire parallel digital cables. These are used for digital data communications between the PSIA and the instrument.

- Four 50 Ω coax cables each fitted with BNC connectors on both ends. These are used for instrument Master Clock connection and for "Loop-Back" testing.

- Two cable harnesses, each of six 50 Ω coax cables fitted with BNC connectors on one end and dual square pin connectors on the other. These are used for connection to the DUT.

- This manual.

#### **Power Supply**

Use only the power supply provided by Audio Precision (AP part number 4540.0020 or 4540.0051) for powering the PSIA. There is no user-replaceable fuse for either power supply.

#### PN 4540.0020

The PN 4540.0020 DC power supply accommodates mains voltages from 100 VAC to 240 VAC and mains frequencies from 47 Hz to 63 Hz. Maximum current consumption is 0.4 A.

If the power supply ON indicator (a green LED near the AP label) does not light when AC mains power is applied to the DC power supply, verify that the mains power cord is functioning properly. If the ON indicator still does not light, contact Audio Precision for a replacement supply.

#### PN 4540.0051

The PN 4540.0051 DC power supply accommodates mains voltages from 100 VAC to 240 VAC and mains frequencies from 50 Hz to 60 Hz. Maximum current consumption is 1.0 A.

#### **Connecting the PSIA to the instrument**

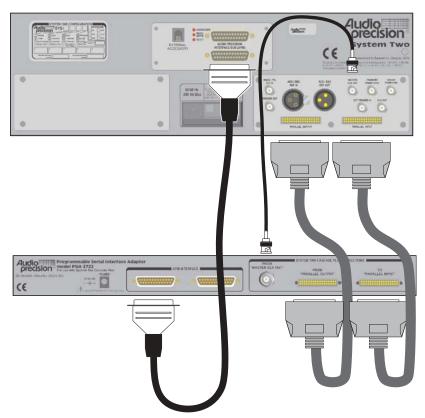

Figure 3. PSIA-2722-to-instrument rear-panel system interconnections.

Place the PSIA near both the instrument and the device that you want to test. Using an APIB cable, connect the instrument to a PC that has AP2700 (or APWIN version 2.22 or 2.24) installed.

Be sure the mains power is OFF for both the instrument and the PSIA. Then connect the four cables between the instrument and the PSIA following these instructions. See Figure 3.

- Attach the APIB cable from one of the PSIA **APIB** connectors to the unused **APIB** connector on the instrument rear panel.

- Connect a 50 Ω BNC cable from the instrument MASTER CLOCK OUT BNC connector to the PSIA rear-panel jack labeled FROM MASTER CLK OUT.

- Connect one 25-wire parallel digital cable from the instrument PARALLEL OUTPUT to the PSIA connector labeled FROM PARALLEL OUTPUT.

- Connect the second 25-wire parallel digital cable from the instrument **PARALLEL INPUT** to the PSIA connector labeled **TO PARALLEL INPUT**.

Finally, insert the 5.5 mm coaxial plug from the 5 VDC power supply into the **POWER** jack on the rear of the PSIA, and plug the mains power cord into the electrical mains supply. This will power up the PSIA and light the **OUT/IN** and **LOGIC VOLTAGE SUPPLY** LEDs.

Switch the instrument ON and launch the control software.

If an APIB cable is connected between the instrument and the PSIA but the PSIA is not powered ON, the control software will start in Demo Mode. Be sure that the PSIA is ON when starting the control software with the APIB cable connected.

If you connect the PSIA to the instrument after the control software has been launched, choose **Utilities > Restore Hardware** to enable the software to recognize the presence of the PSIA.

All four instrument-to-PSIA cables must be connected for the PSIA to operate properly.

### **Chapter 3**

#### **Converter Testing**

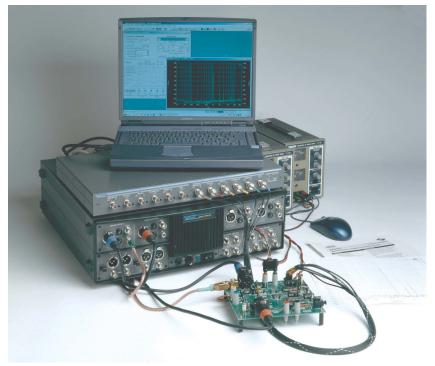

Figure 4. PSIA-2722 with Audio Precision instrument and coverter test fixture.

PSIA-2722 is designed to enable testing of audio analog-to-digital converters (ADCs), digital-to-analog converters (DACs) and other digital devices that have data or clock characteristics that are not compatible with the AES3 / IEC60958 (also called AES/EBU and SPDIF) digital serial interface standards.

The AES3 and IEC60958 standards limit the audio data word length and format, number of channels, sample rates, and sychronization relationships to

a narrow range of choices. These standards also specify the addition of metadata and the superimposition of clock rate and data into one stream by use of bi-phase mark encoding.

The PSIA transmitter and receiver are unconstrained by these standards. Each section has five clock ports and one data port, enabling common threeor four-wire serial interfacing. Each section can be operated in a master or slave relationship with the DUT. Clock relationships and clock-to-data relationships are variable, and with an additional master clock generator the transmitter and receiver sections can be set to different sample rates for SRC testing.

This chapter provides an overview of digital converter testing with an Audio Precision instrument and the PSIA-2722, including connection diagrams and PSIA software panel operation. Examples of actual converter setups are detailed on the Audio Precision Web site. See Appendix B for more information about test configuration examples and sample files.

#### Relationship between PSIA and the instrument

The PSIA-2722 has no function without an Audio Precision instrument. All signal generation and analysis, DSP processing, and computer control operations such as file handling, data display, etc., are performed by the instrument.

The instrument digital or analog audio generators and analyzers selected for a particular test will be used with the PSIA in the same way that they would be in testing using the AES3 interface, but PSIA functions replace the instrument's internal AES3 transmitter/receiver.

See Chapter 2 for information on interconnecting the instrument hardware with the PSIA.

### ኯኯ

The control software provides two PSIA software panels for serial interface operation. Click on the PSIA **Transmitter** (green) or PSIA **Receiver** (red) buttons on the Toolbar, or choose **Panels > PSIA Transmitter** or **Panels > PSIA Receiver** on the Main menu or press **Ctrl-T** or **Ctrl-R** to open the panels.

Next open the DIO panel by clicking the DIO button or by choosing **Panels** > **Digital Input/Output**. Enable PSIA operation for input or output by selecting **PSIA** as the DIO **Input: Connector** or **Output: Connector** (APWIN: **Input: Format** or **Output: Format**) setting.

A number of DIO panel controls and displays also affect the PSIA; for convenience, some of these controls and displays are duplicated on the PSIA panels. See **Duplicated Displays and Controls** on page 19.

#### **PSIA Transmitter and Receiver Connections**

Figure 6. The PSIA-2722 front panel.

The PSIA-2722 communicates with the device under test through its frontpanel Transmitter and Receiver ports.

Use the six-cable harnesses provided to connect the PSIA transmitter or receiver to the DUT. If your DUT has BNC connectors rather than square pin connectors, use high-quality 50  $\Omega$  coaxial BNC cables of matched length. Connection diagrams for Loop-Back, ADC testing, DAC testing and SRC testing configurations follow.

#### **Connect an oscilloscope**

It is useful to view the clock and data waveforms simultaneously on a multichannel oscilloscope while configuring and testing the PSIA. Dedicated scope monitoring jacks are provided for each PSIA port. See **Oscilloscope Monitoring** on page 46.

#### **Connections for Loop-Back configuration**

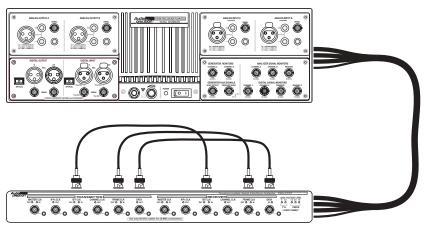

Figure 5. PSIA-2722 in Loop-Back configuration.

Begin each new setup by running a test with the PSIA in a Loop-Back configuration, which requires the use of both the PSIA Transmitter and Receiver sections. Running a test in Loop-Back configuration is a simple way of verifying that your PSIA Transmitter and Receiver settings are compatible, that synchronization and data signals are passing properly through the PSIA, and that the instrument Generator, Analyzer, DIO settings and test parameters are appropriate for PSIA use. Set up a Loop-Back test by following these steps:

- On the DIO panel, choose PSIA in both the Input: Connector (APWIN: Input: Format) list and the Output: Connector (APWIN: Output: Format) list. This will enable both Transmitter and Receiver panels.

- Open both the PSIA Transmitter and Receiver panels.

- Connect three loop-back cables between the PSIA Transmitter and Receiver Bit Clock, Frame Clock and Data ports. See Figure 5.

- Run a simple test through the PSIA loop-back. This will verify that the PSIA is connected correctly and that your test is compatible and properly configured.

A typical "simple test" might be a 1 kHz sine wave from the Digital Generator routed to the PSIA via the DIO Output setting, then brought back into the instrument from the PSIA via the DIO Input setting and routed into the FFT analyzer where a frequency-domain graph is created.

In a **New Test,** the PSIA Transmitter and Receiver sections have compatible settings by default, ready for a loop-back test.

• With the loop-back cables connected, re-set the PSIA controls for the data configuration, clock rates and logic voltages required for testing your DUT. Run your test again to verify that the test is still compatible and properly configured for these new settings.

#### **Connections for ADC testing**

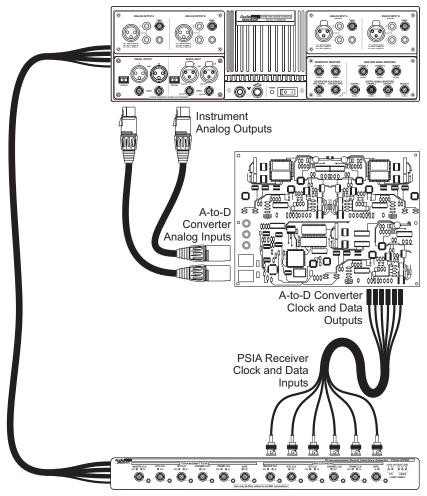

Figure 7. ADC testing with the PSIA-2722.

First, set the PSIA LOGIC VOLTAGE LEVEL (see page 33) to the correct voltage setting for the logic circuits in the ADC.

For analog-to-digital converter (ADC) testing, the instrument provides stimulus signals directly to the ADC in the analog domain and analyzes the device output in the digital domain via the PSIA receiver and the instrument's DIO.

Set any jumpers or switches necessary for the test on your DUT. Connect your DUT to the proper PSIA ports and make any other direct audio or digital connection from the DUT to the instrument necessary for your test, as shown in Figure 7. Many device tests will not require all the available PSIA connections. In most cases, only the Data, Frame Clock and Bit Clock connections are necessary.

Make your generator and analyzer settings compatible with the characteristics of your device.

Apply power to the DUT.

#### **Connections for DAC testing**

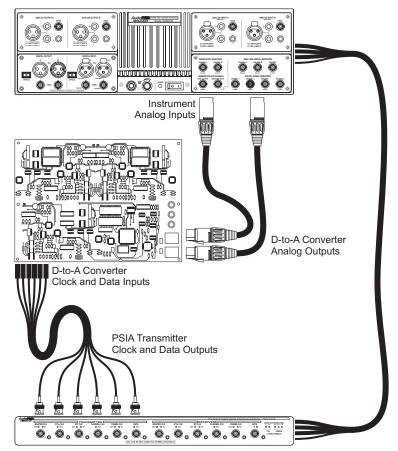

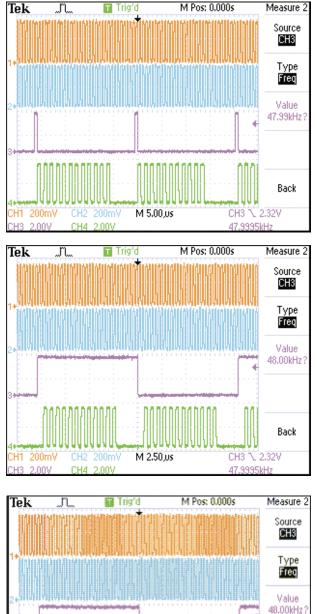

Figure 8. DAC testing with the PSIA-2722.

First, set the PSIA LOGIC VOLTAGE LEVEL (see page 33) to the correct voltage setting for the logic circuits in the DAC.

For digital-to-analog converter (DAC) testing, the instrument provides stimulus signals in the digital domain via the DIO and the PSIA Transmitter, and directly analyzes the device output in the analog domain. Only the PSIA Transmitter panel is needed for DAC testing, and the PSIA Receiver panel may be closed. If you have another use for the DIO Input, you may de-select **PSIA** in the **Input: Connector** (APWIN: **Input: Format**) list.

Set any jumpers or switches necessary for the test on your DUT. Connect your device to the proper PSIA ports and make any other direct audio or digital connection from the DUT to the instrument that is necessary for your test, as shown in Figure 8. Many device tests will not require all the available PSIA connections. In most cases, only the Data, Frame Clock and Bit Clock connections are necessary.

Make your generator and analyzer settings compatible with the characteristics of your device.

Apply power to the DUT.

#### **Connections for SRC testing**

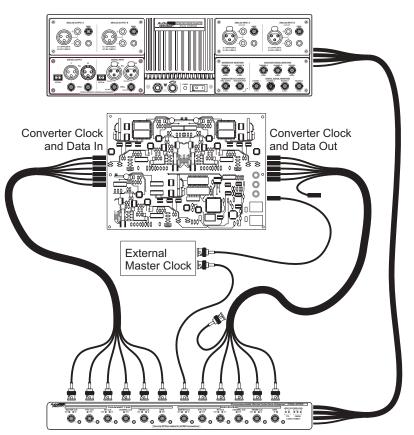

Figure 9. SRC testing with the PSIA-2722.

First, set the PSIA LOGIC VOLTAGE LEVEL (see page 33) to the correct voltage setting for the logic circuits in the SRC.

A sample rate converter (SRC) has digital inputs and outputs and does not require analog generation or analysis capability. For SRC testing, the instrument provides stimulus signals in the digital domain via the DIO and the PSIA Transmitter, and analyzes the device output in the digital domain via the PSIA receiver and the DIO.

For SRC and Loop-Back testing, both the PSIA Transmitter and Receiver panels are necessary. You will need to keep **PSIA** as the selection in both the DIO **Input: Connector** and **Output: Connector** (APWIN: **Input: Format** and **Output: Format**) lists.

Set any jumpers or switches necessary for the test on the SRC. Connect the SRC to the proper PSIA ports for your test, as shown in Figure 9. Many device tests will not require all the available PSIA connections. In most cases, only the Data, Frame Clock and Bit Clock connections are necessary.

In SRC testing the PSIA Transmitter and Receiver may be set to sample rates that are not the same: the transmitter may be required to operate at 48 kHz, for example, while the receiver must be set to 44.1 kHz. When using only the instrument/PSIA master clock, dual sample rates are constrained to certain ranges and ratios. For other combinations of sample rate, a second external master clock must be used.

Make your generator and analyzer settings compatible with the characteristics of your device.

Apply power to the DUT.

\_ 🗆 ×

Pad 8 bit

omputed Rate

0 0

C  $\odot$

#### **The Transmitter and Receiver panels**

The PSIA Transmitter and Receiver panels are very similar. Figures 10 and 11 show the two panels. The settings and displays are discussed below as they apply to both panels, with the exceptions noted.

| PSIA Serial Interface Tran            | smitter                      |                         |                        | _                                 |           | Eigun                                 | ~ 1     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | The                  |                   | 1                  |        |                  |

|---------------------------------------|------------------------------|-------------------------|------------------------|-----------------------------------|-----------|---------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------|--------------------|--------|------------------|

| Channel Data Assignment               |                              |                         | Channel E              | Data Structure                    |           | Figur                                 |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   | IA                 |        |                  |

| Generator Channel A                   | В                            | 0                       |                        | >                                 | 31        | Trans                                 | smi     | ter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <sup>-</sup> ра      | nel.              |                    |        |                  |

| Data criannei                         | 1                            | -                       |                        | First 🔽                           |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| I2S Loop-Back Rise                    | e / Fall                     | Pad<br>0 bit            |                        | ata Pa                            | d<br>bits |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Transmit Data Clock C                 | ۲                            | Low                     |                        | Bits 💌 8<br>ustify R Low          |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| PreEmphasis: Off                      | <b>V</b>                     | Trow T                  | <u> </u>               |                                   |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Scale Freq. By: Output Rate           | <u>-</u>                     |                         |                        |                                   |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Rate Ref: 48.0000 kHz                 |                              |                         |                        |                                   |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Clocks Direction E                    | Bit Clock<br>dge Sync Invert | Shift Bit<br>1 bit Wide |                        | Compute                           | d         |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Frame Clock (Fs)                      | Rise / Fall Wfm              | left Pulse              | Setting<br>48.0000 kHz | Rate<br>= 48.0000 kHz             |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Channel Clock                         | о е п                        |                         | ·                      | annels = 96.0000 kH;              | _         |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| (Subframe Clock) 001<br>Bit Clock © C |                              |                         | x 32 bits<br>cha       | :/ = 3.07200 MH                   | z         |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| N*Fs OUT                              |                              |                         | 256 x F:               | s = 12.2880 MH                    | z         |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Master Clock. Tx Out, Rx              | in 💌                         |                         | × F:                   | s = 12.2880 MH                    | z         |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

|                                       |                              | oltage Level            |                        |                                   |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

|                                       | 5V<br>                       | 3.3 V                   | 3.3 V 2                | 4V 1.8V                           |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

| Commence                              | 0                            | 0                       | •                      |                                   |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |

|                                       |                              | TTL                     | CMC                    | DS                                |           |                                       |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |                   |                    |        |                  |